Mealy vs. Moore Machines

Moore: Output depends on current state

only.

Mealy: Output depends on current state

and input.

For Mealy Output:- Output is function of state n inputs. Specifies state on transition arc.

For Moore Output:- Output is only function of State. Specifies state bubble in state diagram.

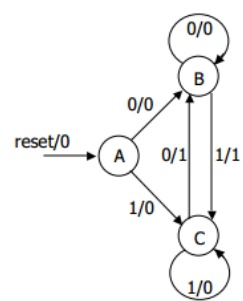

MEALY STATE MACHINE EXAMPLE:

module ED_Mealy (

input reset,

input clk,

input in,

output reg out

);

parameter A = 3'b000; //0

parameter B = 3'b001; //1

parameter C = 3'b010; //2

reg [2:0] state; // Current state

reg [2:0] nxtState; // Next state

always @(posedge clk)

begin

if (reset)

state <= A; // Initial state

else

state <= nxtState;

end

always @(*)

begin

nxtState = state;

out = 0;

case (state)

A :

if (in)

nxtState = C;

else

nxtState = B;

B :

if (in)

begin

out = 1;

nxtState = C;

end

C :

if (~in)

begin

out = 1;

nxtState = B;

end

default :

begin

out = 1'bx;

nxtState = 3'bx;

end

endcase

end

endmodule

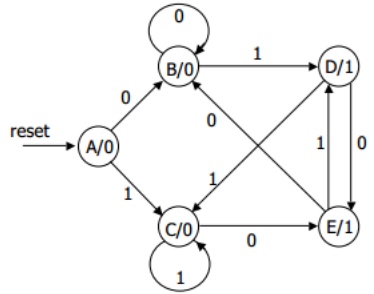

MOORE STATE MACHINE:

module ED_Moore (

input reset,

input clk,

input in,

output reg out

);

parameter A = 3'b000; //0

parameter B = 3'b001; //1

parameter C = 3'b010; //2

parameter D = 3'b100; //4

parameter E = 3'b101; //5

reg [2:0] state; // Current state

reg [2:0] nxtState; // Next state

always @(posedge clk)

begin

if (reset)

state <= A; // Initial state

else

state <= nxtState;

end

always @(*)

begin

nxtState = state;

out = 0;

case (state)

A :

if (in)

nxtState = C;

else

nxtState = B;

B :

if (in)

nxtState = D;

C :

if (~in)

nxtState = E;

D :

begin

out = 1;

if (in)

nxtState = C;

else

nxtState = E;

end

E :

begin

out = 1;

if (in)

nxtState = D;

else

nxtState = B;

end

default :

begin

out = 1'bx;

nxtState = 3'bx;

end

endcase

end

endmodule

STIMULUS:

module ED_tb;

reg reset, clk, in;

wire out;

integer i;

ED_Mealy ED_Mealy_inst (

.reset (reset ),

.clk (clk ),

.in (in ),

.out (out )

);

always

#5 clk = ~clk;

initial

begin

clk = 0;

reset = 1;

in = 0;

repeat(5)

@(posedge clk);

reset = 0;

@(posedge clk);

for (i=0;i<=20;i=i+1)

begin

in = $random;

@(posedge clk);

end

$stop;

end

endmodule