Asynchronous Up-Down 8-bit Counter.

Module

module up_down_counter(q_out,co,Count,incriment,clk,clr);

output [7:0]q_out;

output co;

input clk,clr,Count,incriment;

reg [7:0] q_out;

assign co = Count & (q_out == 8'b11111111);

always @(posedge clk & negedge clr)

begin

if(~clr)

begin

q_out <= 8'b00000000;

end

else if (Count)

begin

if(incriment)

begin

q_out <= q_out+1'b1;

end

else

begin

q_out <= q_out-1'b1;

end

end

else

begin

q_out <= q_out;

end end

endmodule

////////////////////////////////////////////////////////

Stimulus

module stimulus;

wire co;

wire [7:0] q_out;

reg count,clk,clr,incriment;

up_down_counter c1(q_out,co,count,incriment,clk,clr);

initial

begin

clk=1'b0;

forever

#1 clk = ~clk;

end

initial

begin

clr=0;count=1;incriment=1;

#10 clr=1;count=1;incriment=1;

#10 clr=1;count=1;incriment=0;

#10 clr=1;count=0;incriment=1;

#10 clr=0;count=1;incriment=1;

#10 $stop;

#10 $finish;

end

endmodule

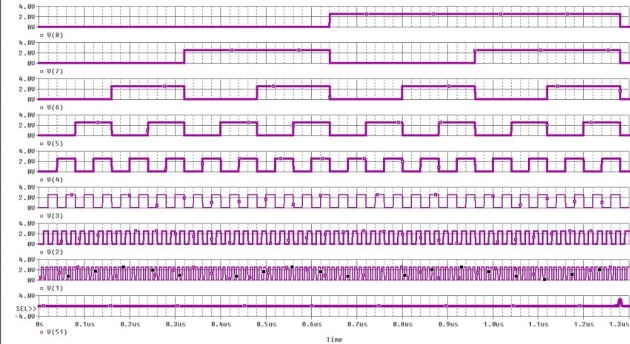

Output