module shiftreg(out_put, in, s1, s2, msb_in, lsb_in, clk, clr);

output [3:0] out_put; reg [3:0]out_put;

input [3:0] in;

input s1;

input s2;

input msb_in;

input lsb_in;

input clk;

input clr;

always @ (posedge clk or negedge clr)

if(~clr)

out_put<=4'b0000;

else

case ({s1, s2})

2'b00:out_put<=out_put;

2'b01:out_put<={msb_in,out_put[3:1]};

2'b10:out_put<={out_put[2:0],lsb_in};

2'b11:out_put<=in;

endcase endmodule

module Stimulus;

wire [3:0] A_out_put;

reg clk, clear, sleft, sright;

reg s2,s1;

reg [3:0] I_in;

//Module Instantiation

shiftreg u0(A_out_put, I_in,s2,s1,sright,sleft, clk,clear);

initial

begin

clk=1'b0;

forever

#1 clk = ~clk;

end

//Values checking part

initial

begin

s2=0;s1=0; I_in=4'b1111; clear=0; sleft=0; sright=1;

#5 s2=1;s1=0; I_in=4'b1111; clear=0; sleft=0;sright=1;

#5 s2=1;s1=0; I_in=4'b1111; clear=1;sleft=0;sright=1;

#5 s2=0;s1=1;I_in=4'b1111; clear=1; sleft=1;sright=0;

#5 s2=1;s1=1; I_in=4'b1011; clear=1;sleft=0; sright=0;

#5 s2=1;s1=1; I_in=4'b1100; clear=1;sleft=0;sright=0;

#5 s2=1;s1=1; I_in=4'b0011; clear=0;sleft=0; sright=0;

#10 $sshiftreg;

#10 $finish;

end

endmodule

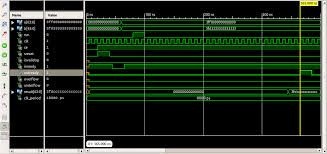

output