implement a 4x16 Decoder

Module

module decoder(d,w,x,y,z,);

input w,x,y,z;

output [15:0]d;//vector haiving 16 number of bits

assign d[0]= (~x) & (~y) &(~z) & (~w) ;//make 16 combinations of input

assign d[1]= (~x) & (~y) &(~z) & (w) ;

assign d[2]= (~x) & (~y) &(z) & (~w) ;

assign d[3]= (~x) & (~y) &(z) & (w) ;

assign d[4]= (~x) & (y) &(~z) & (~w) ;

assign d[5]= (~x) & (y) &(~z) & (w) ;

assign d[6]= (~x) & (y) &(z) & (~w) ;

assign d[7]= (~x) & (y) &(z) & (w) ;

assign d[8]= (x) & (~y) &(~z) & (~w) ;

assign d[9]= (x) & (~y) &(~z) & (w) ;

assign d[10]= (x) & (~y) &(z) & (~w) ;

assign d[11]= (x) & (~y) &(z) & (w) ;

assign d[12]= (x) & (y) &(~z) & (~w) ;

assign d[13]= (x) & (y) &(~z) & (w) ;

assign d[14]= (x) & (y) &(z) & (~w) ;

assign d[15]= (x) & (y) &(z) & (w) ;

endmodule

Stimulus

module decoder2;

wire d;

reg w,x,y,z;

decoder d1(d,w,x,y,z); //instantion of main module

initial

begin

x=0; y=0; z=0; w=0; //apply all combination of input

#10 x=0; y=0; z=0; w=1;

#10 x=0; y=0; z=1; w=0;

#10 x=0; y=0; z=1; w=1;

#10 x=0; y=1; z=0; w=0;

#10 x=0; y=1; z=0; w=1;

#10 x=0; y=1; z=1; w=0;

#10 x=0; y=1; z=1; w=1;

#10 x=1; y=0; z=0; w=0;

#10 x=1; y=0; z=0; w=1;

#10 x=1; y=0; z=1; w=0;

#10 x=1; y=0; z=1; w=1;

#10 x=1; y=1; z=0; w=0;

#10 x=1; y=1; z=0; w=1;

#10 x=1; y=1; z=1; w=0;

#10 x=1; y=1; z=1; w=1;

#10 $stop;

#10 $finish;

end

endmodule

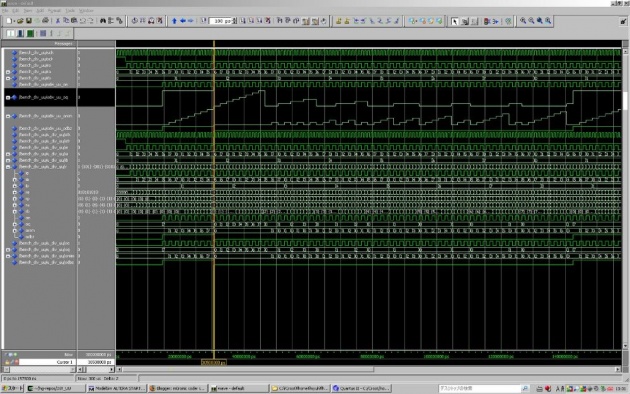

Output